驱动电路板作为电子设备的核心控制单元,其成本控制对产品量产效益与市场竞争力有着关键影响。驱动电路板成本优化并非简单的材料替换或工艺简化,而是通过科学的元器件选型与合理的多层板叠构设计,在保障性能指标与可靠性的前提下,实现成本与品质的动态平衡。本文从这两个核心维度展开,剖析驱动电路板成本优化的关键路径。

元器件选型:成本与性能的精准匹配

元器件在驱动电路板总成本中占比超过六成,选型环节的决策决定成本基数。选型工作需建立在对电路功能需求精准拆解的基础上,摒弃“超额设计”惯性,实现性能适配与成本控制的统一。

规格参数的精准把控是选型的首要前提。驱动电路中,功率器件、逻辑芯片等核心元器件的参数冗余是成本浪费的主要源头。需结合电路的额定电流、电压波动范围、工作温度区间等实际工况,确定元器件的关键参数阈值。例如功率管选型,需通过电路仿真得出实际工作时的最大耗散功率与峰值电流,以此为依据选择参数达标的器件,避免为追求“余量充足”而选用更高规格的产品。同时,优先选择市场流通量大的标准规格元器件,这类器件因规模化生产效应,单价通常低于特殊规格产品,且供货稳定性更高,可降低后续采购环节的隐形成本。

供应链稳定性与采购成本的协同考量同样重要。选型时需同步调研元器件的市场供应情况,避开独家供应或货源稀缺的器件,这类器件不仅议价能力弱,还可能因供应链波动导致交货延迟。同一功能模块可备选2-3种不同品牌的元器件,通过对比不同供应商的报价、最小起订量及交货周期,建立性价比评估体系。对用量较大的阻容元件、接口芯片等,可与供应商协商长期供货协议,通过批量采购获取价格优惠,同时降低物料短缺风险。

多层板叠构:工艺与成本的合理平衡

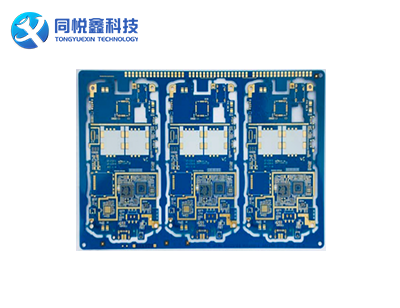

多层板的叠构设计关系到电路的信号完整性、散热性能与制造成本。合理的叠构方案需在满足电路功能需求的基础上,简化工艺步骤、减少材料消耗,实现驱动电路板成本优化。

层数的科学确定是叠构设计的核心。驱动电路板的层数需根据信号密度、布线复杂度及电磁兼容性要求综合判定。并非层数越多性能越优,额外的层数会增加基板材料、覆铜、钻孔等环节的成本,同时延长生产周期。可通过信号分类梳理,将高频信号、功率信号与低速控制信号进行分区规划,在保障信号隔离的前提下,尝试用较少层数实现布线需求。例如,对普通工业驱动电路,可采用4层板替代6层板,通过优化顶层与底层的信号布局,将电源层与接地层合理分配至中间层,既满足绝缘要求,又降低制造成本。

叠层结构的细节优化同样不可忽视。层间介质厚度的选择需结合阻抗匹配要求,避免为追求统一厚度而采用特殊规格的基板材料。优先选用行业通用的介质厚度标准,降低材料采购成本与加工难度。钻孔工艺的成本控制也需重视,叠构设计时应尽量减少盲孔、埋孔的使用,这类孔的加工精度要求高,会增加钻孔时间与废品率。在满足布线连通性的前提下,多用通孔替代,同时将同类孔径的孔集中规划,便于批量钻孔加工,提升生产效率。

驱动电路板成本优化是一项系统性工作,元器件选型与多层板叠构设计是其中的关键环节。选型工作需立足实际工况,实现参数精准匹配与供应链协同;叠构设计需兼顾性能与工艺,通过层数优化与细节把控降低成本。成本优化的核心在于“精准匹配”,既不牺牲产品可靠性与性能指标,也不产生不必要的成本浪费。通过持续优化设计方案与供应链管理,可实现驱动电路板成本与品质的双重提升。